The eProcessor project is an ambitious combination of processor design, based on the RISC-V open source hardware ISA, applications and system software, bringing together multiple partners to leverage and extend pre-existing Intellectual Property (IP), combined with new IP that can be used as building blocks for future HPC systems, both for traditional and emerging application domains. As such, the eProcessor project’s overall goal is to create an open source full stack ecosystem (both software and hardware) by achieving the following objectives:

- Extend open source to include open source hardware for HPC: The eProcessor technology will be based on the RISC-V open source instruction set architecture (ISA) and will feature high performance computing and data analytics accelerators coupled to a high performance, low energy out-of-order processor (Europe’s first high performance out-of-order 64-bit RISC-V platform). This is a major first step in the direction of an open European software/hardware ecosystem, which will guarantee technology independence.

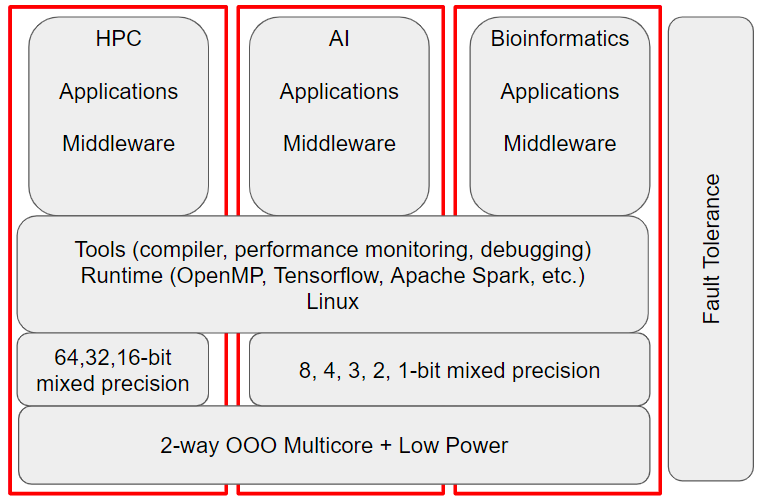

- Software/hardware co-design for improved application performance and system energy efficiency: eProcessor will meet the performance and energy requirements of new and existing HPC applications. eProcessor will co-design solutions to provide high performance, low-power, and fault tolerance. Uniquely, the project will specialize all components of the system in the context of a broad application domain: a combination of energy efficient accelerators, adaptive on-chip memory structures, and a flexible and high performance energy-efficient CPU, with the corresponding open source software stack.

- HPC and HPDA applications: eProcessor will use a diverse set of applications in HPC and high performance data analytics (HPDA, which includes Artificial Intelligence (AI), Deep Learning (DL), Machine Learning (ML) and Bioinformatics applications to drive the design of the overall system. eProcessor will extend these applications and their frameworks to sup-port the RISC-V ISA.

- Focus on sustained application performance: Many HPC and HPDA applications use sparse data sets and/or low/mixed-precision. Instead of focusing on the peak performance of dense computations, eProcessor targets a broader collection of applications by developing a system targeting sustained application performance.

- Stimulate European collaboration: The eProcessor partners will leverage their existing IP from multiple European projects such as European Processor Initiative (EPI), Low-Energy Toolset for Heterogeneous Computing (LEGaTO), MareNostrum Experimental Exascale Platform (MEEP), POP2 CoE, Tulipp, EuroEXA, Ex-aNeSt and DeepHealth and extend their capabilities and improve the Technical Readiness Level (TRL).

By employing software/hardware co-design, as shown in the figure on the previous page, eProcessor covers the whole system stack from HPC and HPDA applications at the top, down to the processor core with accelerators at the bottom while all levels are mutable so as to enable true, unrestricted co-design.