ExaNoDe designed core technologies for a highly energy efficient and highly integrated heterogeneous compute node directed towards Exascale computing. ExaNoDe has built a compute node prototype available for collaborative working comprising:

- Technology and design solutions for an interposer-based computing device targeting HPC applications,

- Integration of devices in a Multi- Chip-Module (MCM) to increase compute density and take advantage of heterogeneity,

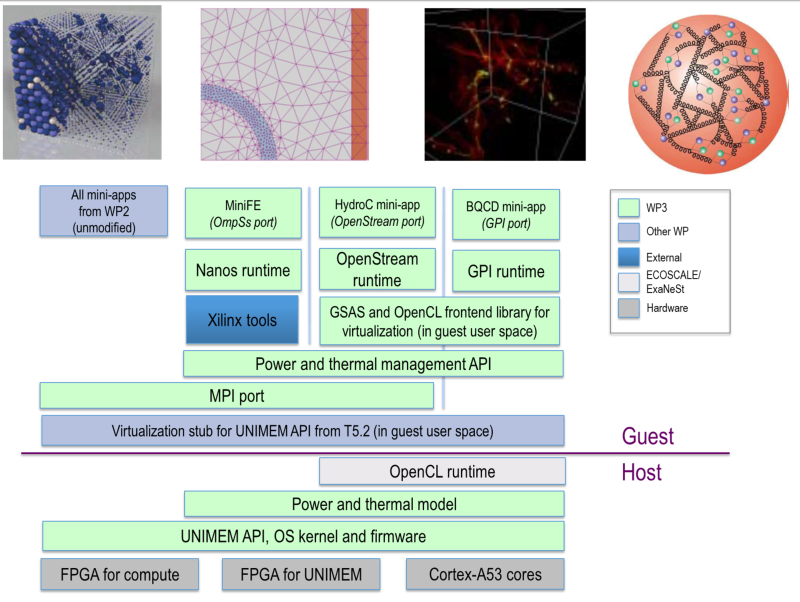

- System and middleware SW stack.

Contribution to Exascale Computing

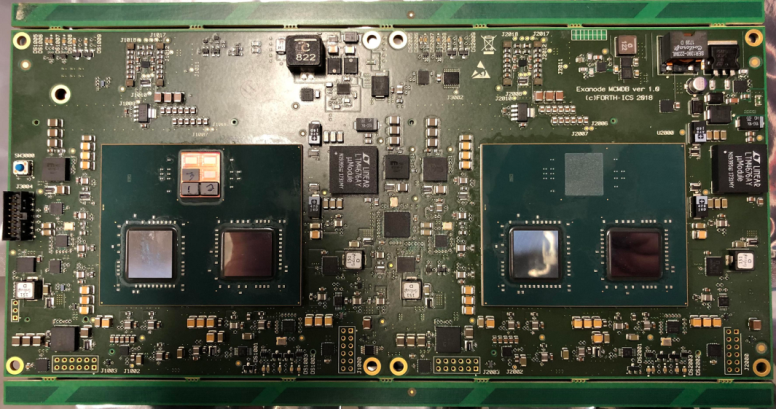

The ExaNoDe final prototype consists of an integrated HW/SW daughter board with two MCMs, each including two chiplets stacked on one silicon interposer and two Xilinx Zynq Ultrascale+ FPGAs. It targets prototype-level use by system integrators, software teams and its subsequent evaluation through industrial deployment. ExaNoDe’s main achievements cover all aspects of heterogeneous integration from silicon technology to system software including:- Design of innovative, high-speed and low-power interconnect for the heterogeneous integration of chiplets via a silicon interposer.

- Design of a Convolutional Neural Network (CNN) accelerator hardware IP for a use case demonstrating heterogeneous integration.

- Design and manufacturing of a chiplet System-on-Chip (SoC) in 28FDSOI technology node

- 3D integration of chiplets on an active silicon interposer with about 50,000 high density (20 µm pitch) connections.

- Advanced package integration with two FPGA bare dies including ARMv8 cores, one interposer and 43 decoupling capacitors in a 68.5 mm ×55 mm Multi-chip-Module (MCM).

- Integration of two MCMs on a 260 mm x 120 mm daughter board. Development of a complete SW stack including UNIMEM-based system software and middleware; Runtimes libraries optimized for the UNIMEM architecture (OmpSs, MPI, OpenStream, GPI); Checkpointing technology for virtualisation; A set of mini-applications for benchmarking purposes.

- A performance projection of ExaNoDe technologies into a strawman architecture representative of upcoming HPC processors.

Previous image

Next image