Now that the Mont-Blanc 2020 project has come to an end, it is time to look back on its accomplishments. Mont-Blanc 2020 was the last of a long series of projects. The initial concept when we started in 2011 was very disruptive: leveraging mobile (Arm) chips and their power-efficiency to run high-performance computing (HPC) applications. Successive Mont-Blanc projects have witnessed and accompanied the rise of Arm processors in servers: the current Fugaku system ranked first in the TOP500 has reached the apex of high-end Arm CPUs, vindicating the initial rationale behind the project.

One of the strong points of the Mont-Blanc projects was their industry / academia collaboration. Mont-Blanc 2020 was no exception, with a team of three core partners with com-plementary profiles (Arm, Atos, BSC), three active SMEs (Kalray, Semidynamics, Sipearl) and prominent research partners (BSC, CEA, Jülich Supercomputing Centre).

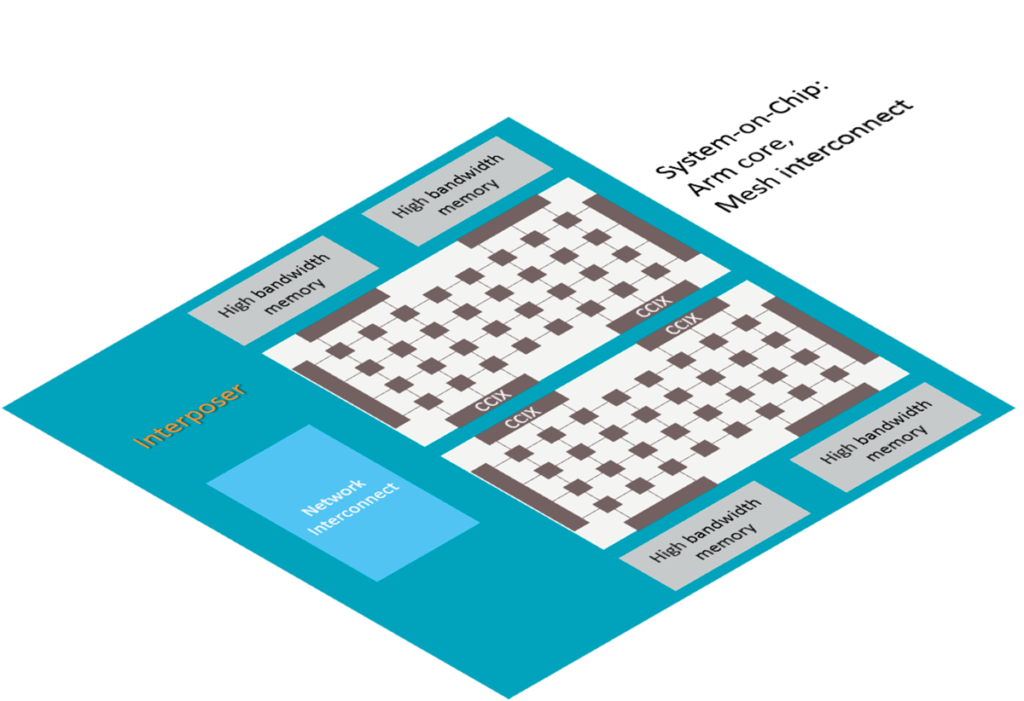

The focus of Mont-Blanc 2020 was processor design. It essentially addressed system-on-chip (SoC) design and processor intellectual property (IP) to enable the work of the Euro-pean Processor Initiative (EPI), focusing on the challenge of achieving extremely high performance per Watt. For the compute unit, we selected the Arm instruction set, with its Scalable Vector Extension (SVE) optimized for HPC and artificial intelligence (AI). It has particular technological relevance for high-end cores; more importantly, the availability of a dynamic software ecosystem was necessary to run real applications as required by our co-design methodology.

An important achievement of Mont-Blanc 2020 is the tools and methodology we select-ed and developed for processor simulation and virtual prototyping, i.e. the tools that allowed our researchers to test applications and evaluate future performance prior to silicon availability. We developed a unique co-design methodology for SoC infrastructure verification and optimization. Co-design is always a challenge, but we faced an addition-al test, which was to get hardware and soft-ware teams from different organizations to work together. We had to build a bridge between the computer-aided design (CAD) tools used by our industrial partners and the open source tools used by our academic partners. Our approach has increased the speed of simulation by a factor of 1,000 and even by 10,000 for some applications.

Many of the features we developed for our Simulation Framework are already used out-side of the project. For example, Mont-Blanc

2020 was instrumental in the implementation of SVE instructions in gem5, which is part of the official open source release 20.0 of gem5. Another example is the SVE-related improvements to the MUltiscale Simulation Approach (MUSA) developed within Mont-Blanc 2020, which are used within EPI.

However, the top Mont-Blanc 2020 achievement is without doubt the IP developed for a low power network on chip (NoC). NoC is critical in a SoC when targeting highly demanding applications. It is also very challenging: in many core architectures you need to maintain low latency while increasing the number of cores as well as the throughput of each core. The NoC IP developed by Mont-Blanc 2020 will be included in the next-generation EPI processor. Our NoC and related NoC IPs are also integrated in Atos’s IP portfolio that will serve future commercial and research projects.

To conclude, European sovereignty in the provision of HPC technology was part of Mont-Blanc’s vision from the start. We aimed to contribute to the revival of the European SoC design ecosystem by creating an IP port-folio as well as boosting the skills necessary for chip design. Today we can say: mission accomplished!