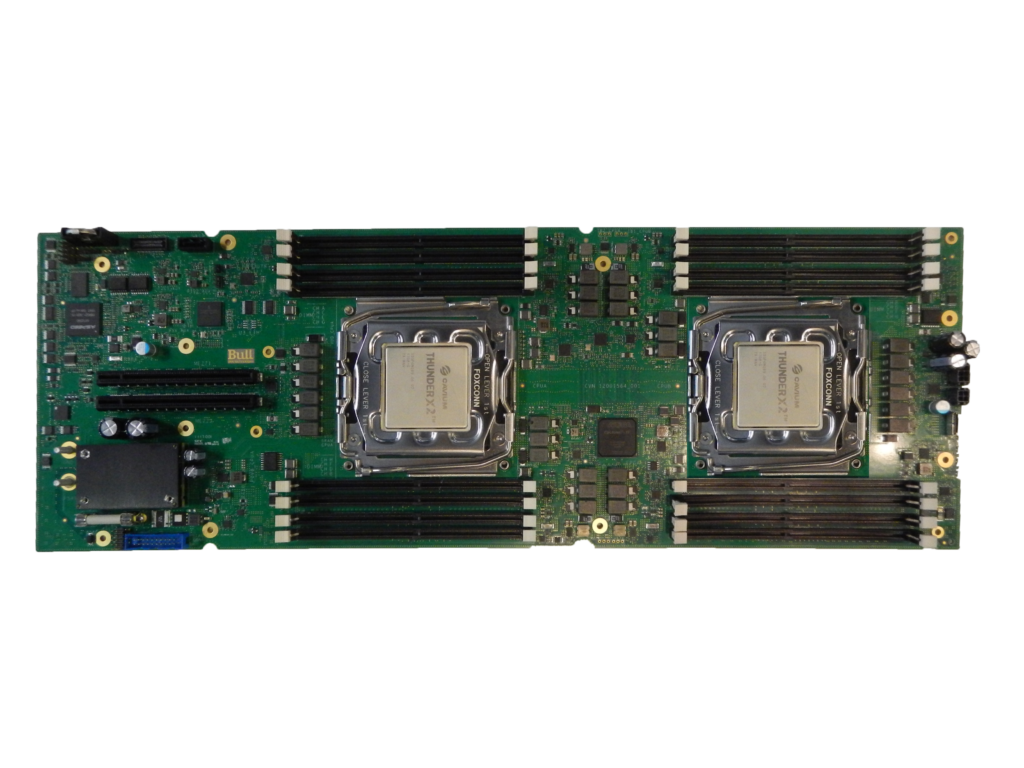

Project Mont-Blanc is now in its third phase. All phases of the Mont-Blanc project share the vision of developing a European Exascale approach leveraging commodity power-and cost-efficient embedded technologies.

The key outcome of the project is the deployment of Arm-based computing platforms enabling Arm architecture in HPC, which boost system software development and allow to test real scientific applications at scale.

Based on the experience gained from the development of various platforms since 2011 and implementing a co-design approach, the Mont-Blanc project now aims to define the architecture of an Exascale-class compute node based on the Arm architecture, and capable of being manufactured at industrial scale.

Our top achievements

- Demonstrating that it is possible to run HPC workloads with European embedded technology

- Contributing to the design of a next-generation exascale-class machine with a co-design approach

- Testing and scaling REAL scientific applications on a non-conventional HPC architecture

Previous image

Next image