The DARE project aims to develop cutting-edge HPC hardware and software based on RISC-V, an open instruction set architecture poised to power exascale and post-exascale supercomputers.

The DARE consortium has been selected to implement a Framework Partnership Agreement (FPA) for developing a large-scale European initiative for a HPC ecosystem based on RISC-V. The FPA will run for six years, until 2030.

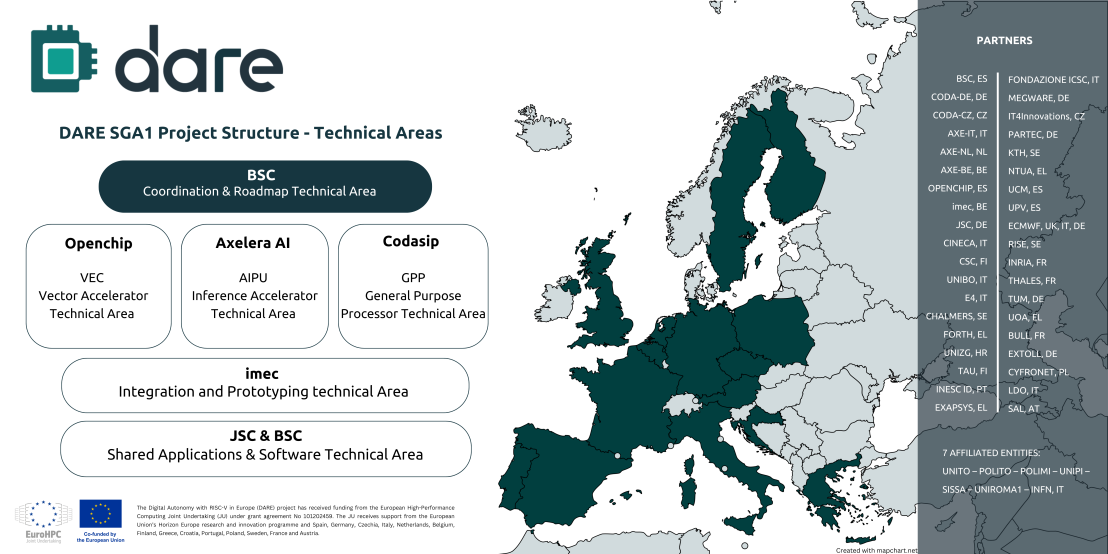

The DARE project is the first Specific Grant Agreement (SGA) for the development of European microprocessors based on RISC-V and cutting edge chiplet technology. It will design, develop, and tape-out in advanced CMOS technology nodes one processor, and two accelerators based on the open RISC-V instruction set architecture. These three components will overcome the limitations of traditional monolithic chips because of their scalability, cost, power, and efficiency trade-off, enabling the creation of truly European products in advanced nodes that aim to power future EuroHPC supercomputers. More precisely, the project will start by designing and developing:

- A general-purpose processor (GPP) optimised for HPC workloads

- A vector accelerator (VEC) for high-precision HPC and emerging applications in the HPC-AI convergence domain;

- An AI Processing Unit (AIPU) designed for AI inference acceleration in HPC applications;

- A supercomputing hardware (HW)/software (SW) stack for HPC and AI

38 partners from 13 countries including SMEs will collaborate as a consortium coordinated by the Barcelona Supercomputing Centre (BSC) to build European cutting-edge HPC hardware and software.

Building on research from EuroHPC JU-funded projects such as the European Processor Initiative (EPI), MEEP, eProcessor, EUPILOT, and EUPEX, DARE is part of the broad European Union’s strategy to reach European autonomy in strategic hardware technologies by investing and building a diverse technology portfolio including processors, (AI) accelerators, quantum chips and other state of the art hardware components.