Our objective is to create a flexible exploration platform for the development and optimization of architectures, tools, and applications targeting Exascale systems using reconfigurable technology. We aim to provide an open-source research platform to enable sustainable research on reconfigurable architectures and tools, and prepare all stakeholders (application, systems, and tool developers) for the emergence of efficient reconfigurable accelerators for Exascale systems. Our work revolves around 5 activities:

Understand the Requirements

We use three different case-studies – Asian option pricing, retinal image segmentation, and Diffusion Monte-Carlo – to investigate the performance, scalability, and energy efficiency challenges that emerge in HPC-like applications at Exascale level. We aim to provide mechanisms to cope with these challenges in both hardware and software.

Design, Develop, and Deploy the Open Research Platform

We focus on the design and implementation of the Open Research Platform, covering its reconfigurability-specific features and design tools. This work includes, for example, research on Virtual Coarse Grained Reconfigurable Arrays (VCGRAs), static and dynamic workload partitioning, efficient data offloading, and parallel memory systems. Furthermore, the CAOS toolchain is developed to support the design and deployment of reconfigurable accelerators, and will integrate the main analysis and optimization tools developed in EXTRA, with support for community extensions in the future.

Research Novel Tools.

We strive to advance the state-of-art compilation tools for reconfigurable hardware, covering just-in-time synthesis, hardware monitoring, emergency management, and hardware debugging.

Investigate Reconfigurable Applications

We search for generalizable optimization opportunities in HPC applications, to leverage reconfiguration, as well as implement, integrate and evaluate their impact on HPC systems.

Propose New Ideas for Reconfigurable Technology

Based on the combined analysis of applications, programming technologies and tools, and hardware platforms, we aim to propose technological improvements that will increase the efficiency of future reconfigurable systems. The main aspects of this activity include the improvement of the reconfiguration process and finding efficient interface solutions for coupling the FPGA fabric and the processing units.

Platform Overview

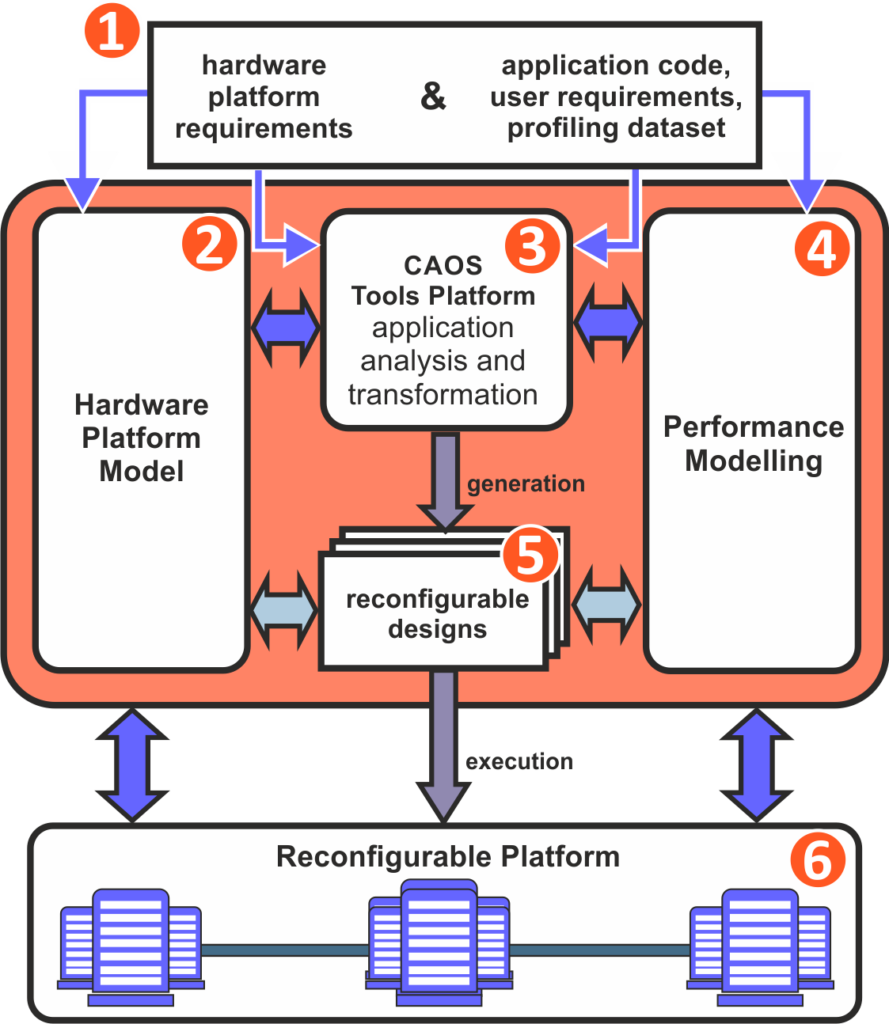

The Open Research Platform has six main components to support the optimization of applications for the next-generation reconfigurable HPC systems. For this purpose, the platform provides an integrated system that combines models for various reconfigurable architectures, tools and applications, allowing researchers to focus on any of these aspects separately or together.

The platform input includes information about the application (e.g., source-code, performance requirements, profiling information) and the specification of the target platform (e.g., size, resources, simulated/hardware). The Hardware Platform Model guides the design and optimization process for a specific target platform. The Tools Platform (e.g., CAOS) generates a reconfigurable design through a set of analysis and transformations steps on the application code. The Performance Modeling component checks the fit of the expected performance with the user requirements at every stage of the development process. One or more candidate reconfigurable design versions is generated to support design-space exploration and select the most suitable implementation to execute on the Reconfigurable Platform, which in turn combines the hardware architecture and runtime of the reconfigurable HPC system.